Projets Partagés

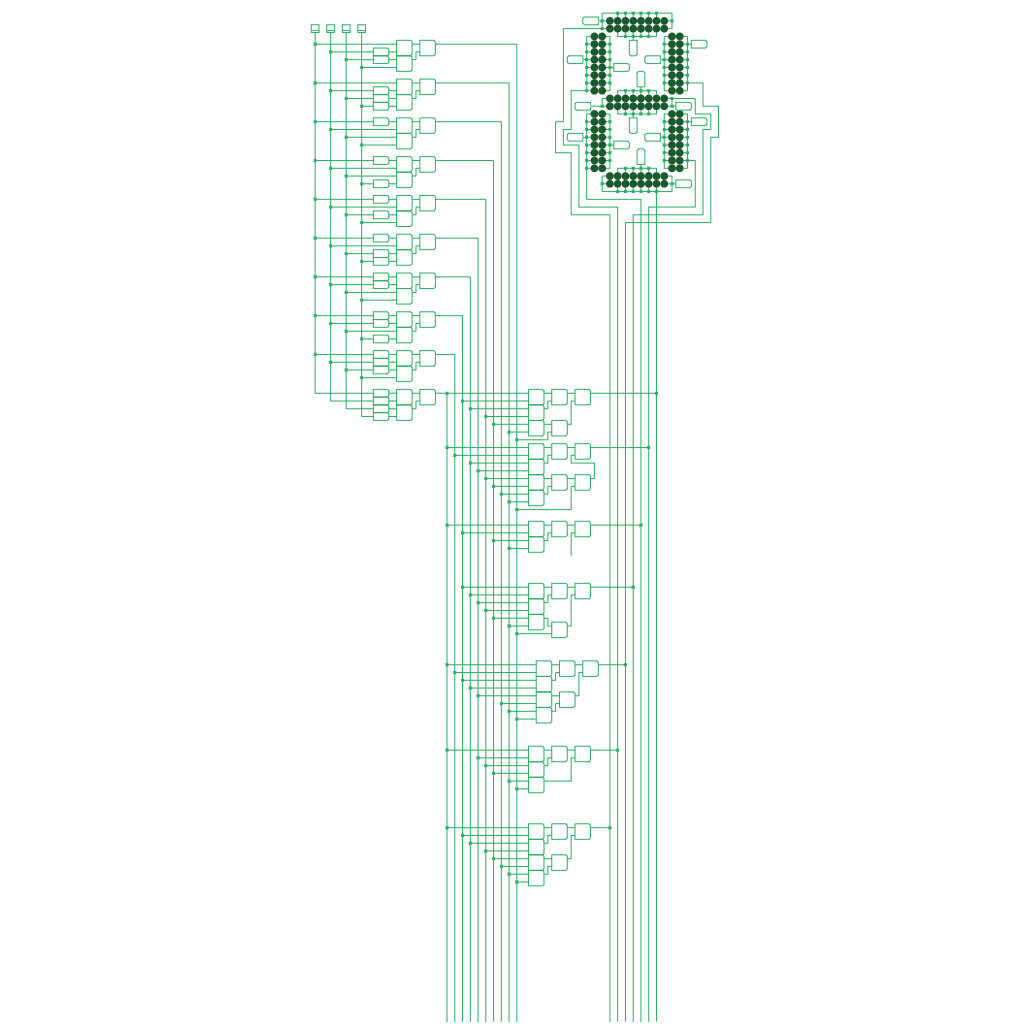

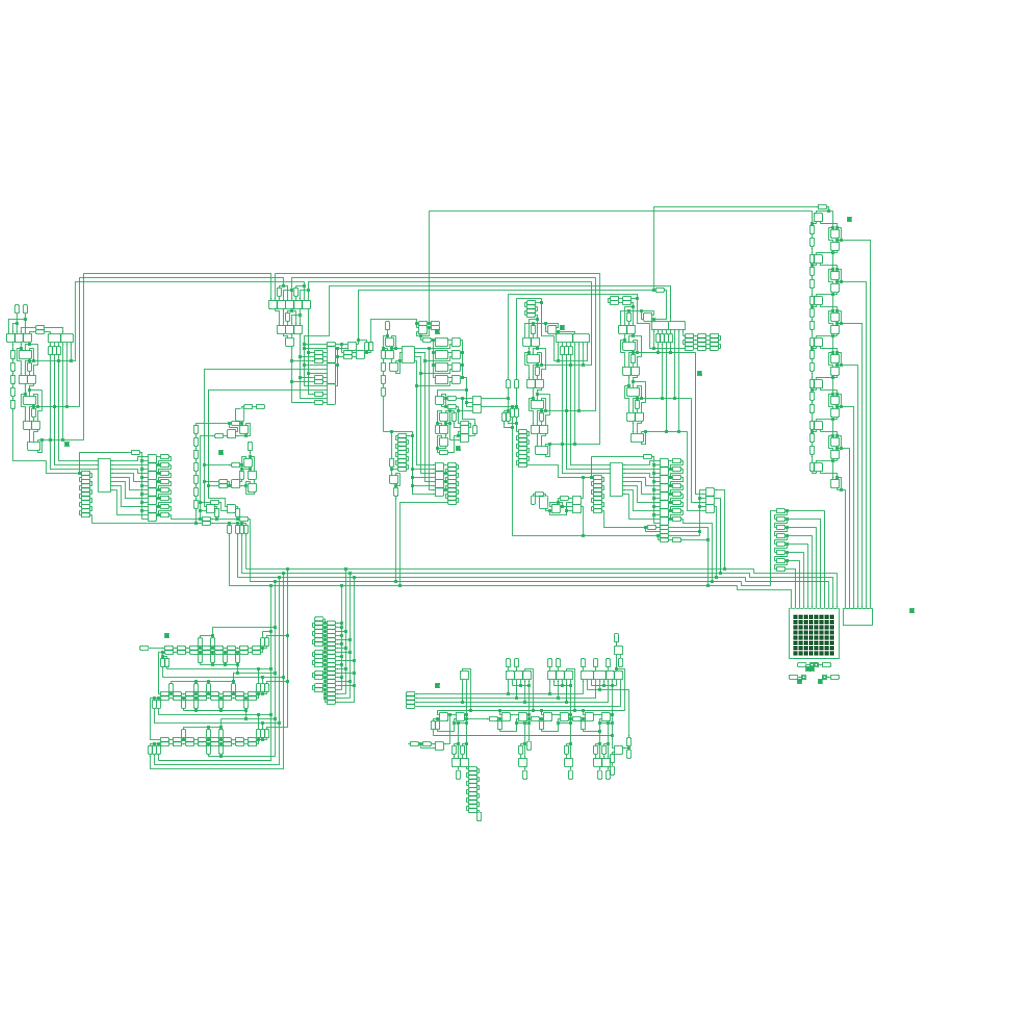

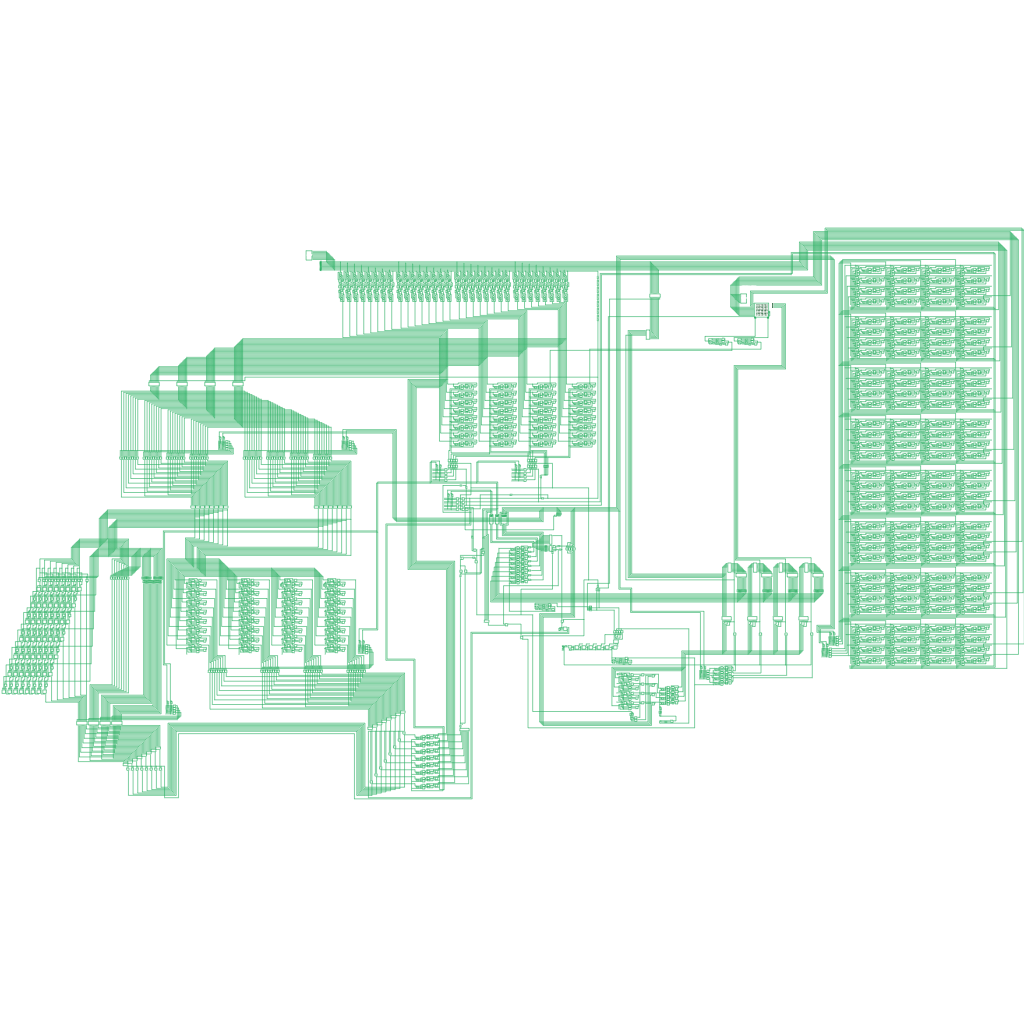

16-Bit General Purpose CPU.

A somewhat better documentation can be found here: https://docs.google.com/spreadsheets/d/1MG44B5RzTul4EMDJowlx4hgNE3XYFRoyR7EFi6A0o3M/edit?usp=sharing

Features:

- Fully programable

- 16 registers

- Up to 128KiB of memory

- Integer operations

- Boolean operations

- Stack

- Function calls

- 16x16 display with basic IO

TODO:

- Serial Bus

- Interrupts

- Finish programming "pong" :)

16-Bit General Purpose CPU.

A somewhat better documentation can be found here: https://docs.google.com/spreadsheets/d/1MG44B5RzTul4EMDJowlx4hgNE3XYFRoyR7EFi6A0o3M/edit?usp=sharing

Features:

- Fully programable

- 16 registers

- Up to 128KiB of memory

- Integer operations

- Boolean operations

- Stack

- Function calls

- 16x16 display with basic IO

TODO:

- Serial Bus

- Interrupts

- Finish programming "pong" :)

im stronger, im faster, i am better. I AM BETTER

Grüße an die Spätschicht :)

Follow the instructions next to the display to play this small simple game.

Auch von mir schöne Grüße an die Spätschicht!

Inhalt:

- XOR Gatter aus Basisteilen

- Halbaddierer aus Basisteilen

- Volladdierer aus Basisteilen

- Volladdierer aus Halbaddierern

- 4-Bit / n-Bit Binär Addierer aus Volladdierern und Halbaddierern

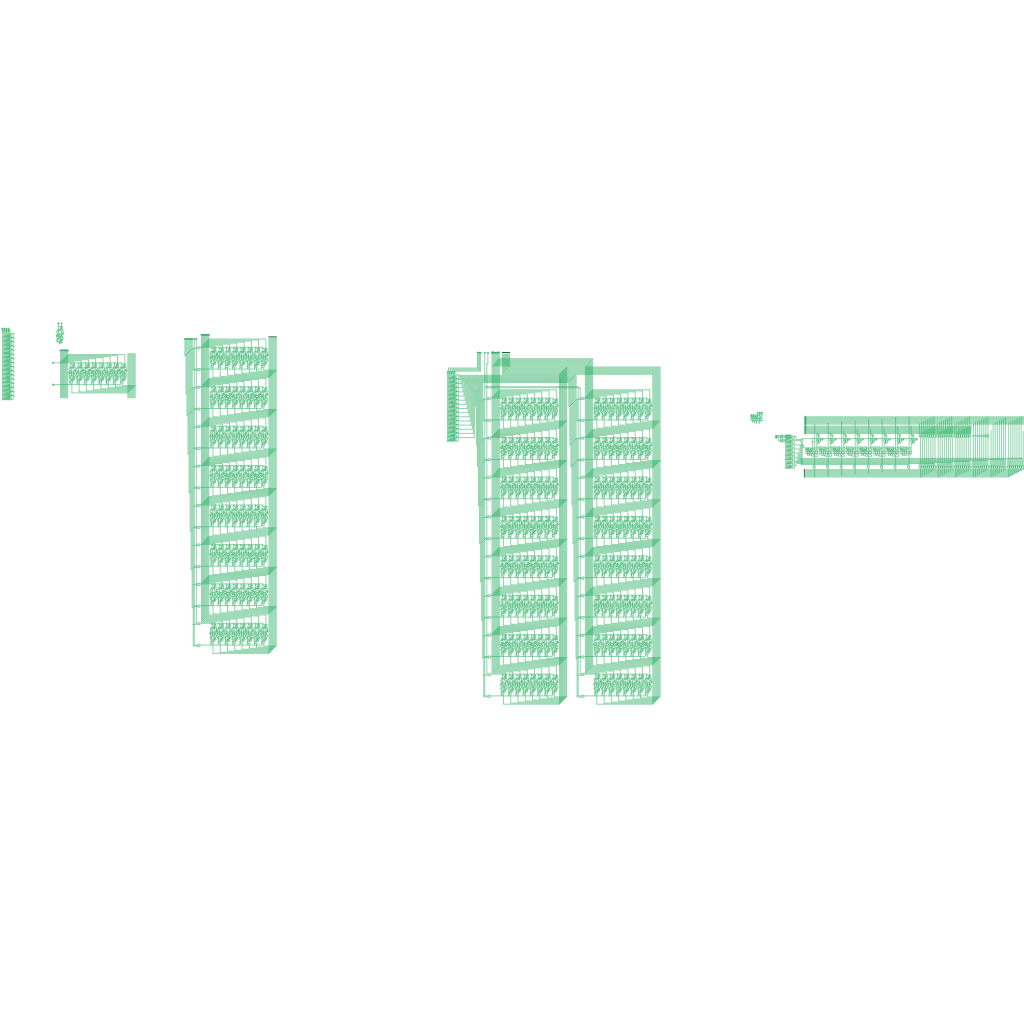

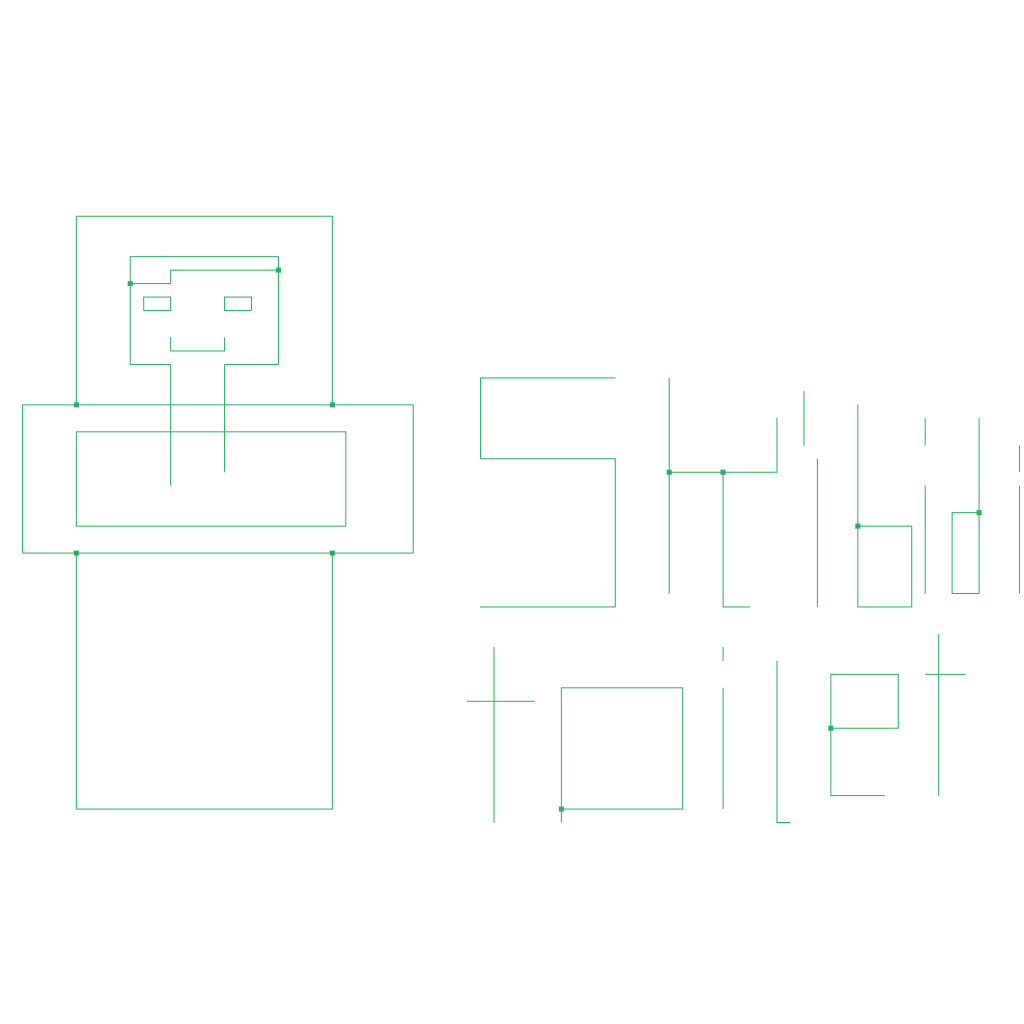

A custom fully programmable 8-BIT CPU.

Very transparent! (You see everything happening!)

I implemented design choices in CPU architecture to

enhance its efficiency, even though it doesn't alter the functionality of

the CPU itself. Basically bringing its theoretical TDP down.

AS FEW ADVANCED GATES AS POSSIBLE!

128 BIT RAM

512 BIT ROM

4 GENERAL PURPOSE REGISTERS

SWAPPABLE ALU (8 OPERATIONS TOTAL)

Higher or lower number game already programmed!

A custom fully programmable 8-BIT CPU.

Very transparent! (You see everything happening!)

I implemented design choices in CPU architecture to

enhance its efficiency, even though it doesn't alter the functionality of

the CPU itself. Basically bringing its theoretical TDP down.

AS FEW ADVANCED GATES AS POSSIBLE!

128 BIT RAM

512 BIT ROM

4 GENERAL PURPOSE REGISTERS

SWAPPABLE ALU (8 OPERATIONS TOTAL)

Higher or lower number game already programmed!

Lyrics:

Couse my style is ridicdicdicdiccoulescoulescoules drrr skibidi dop dop dop yes yes skibidi w dip dip skibidi dop dop dop yes yes skibidi w dip dip, we hear its such a Party skibidi skibidi skibidi....

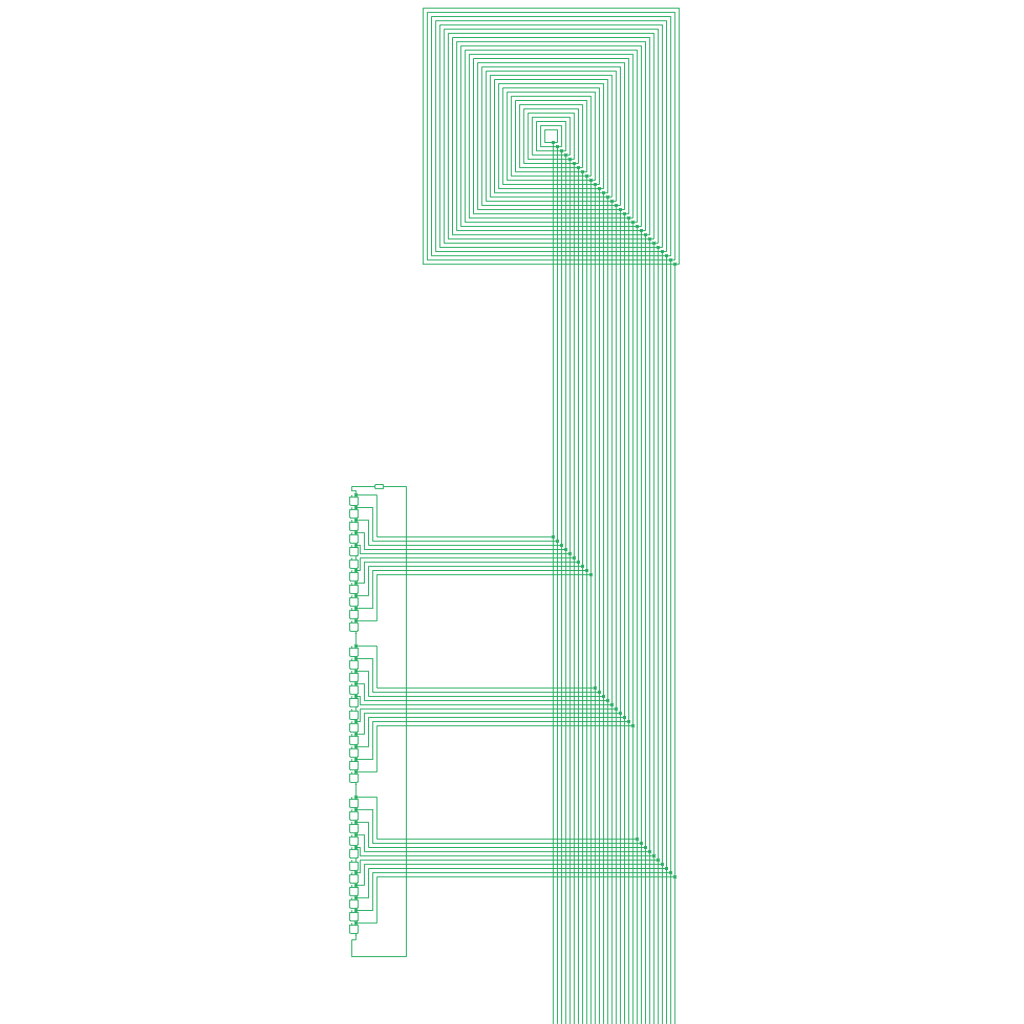

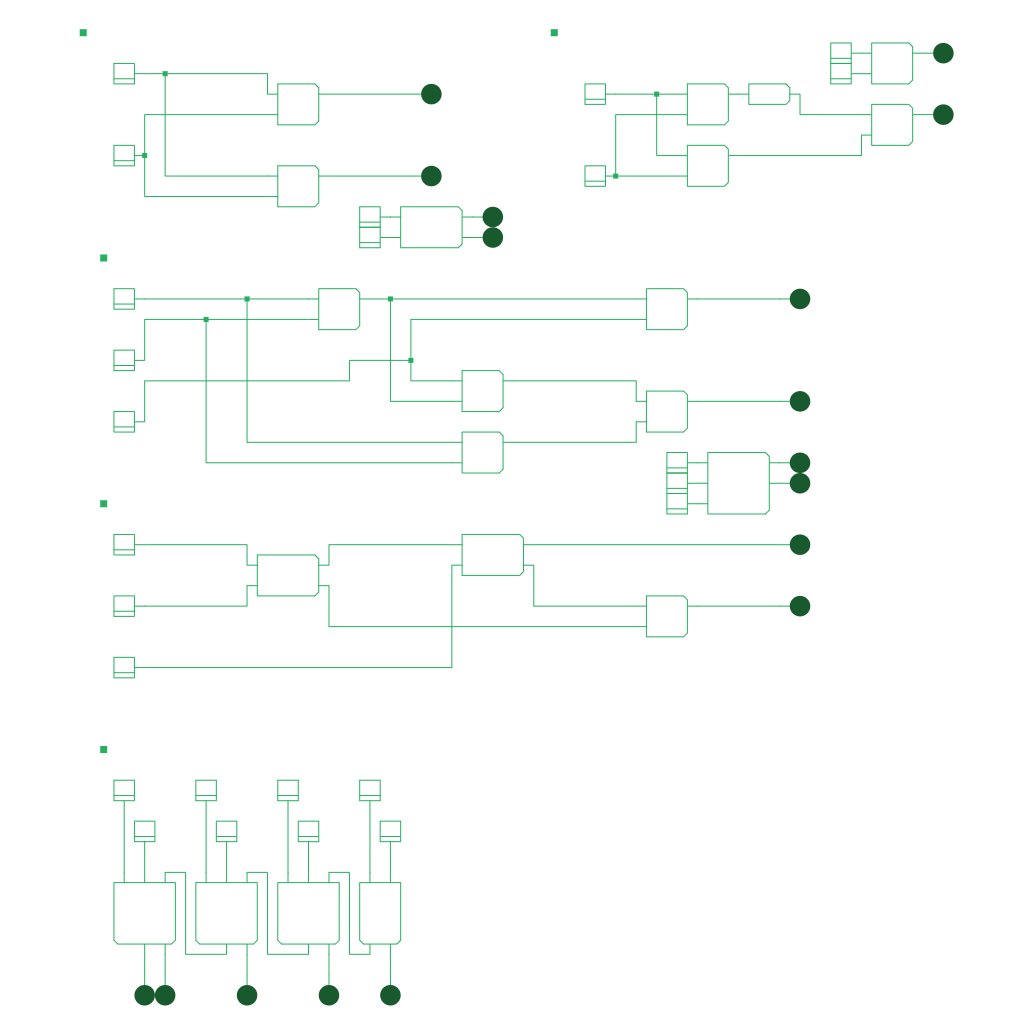

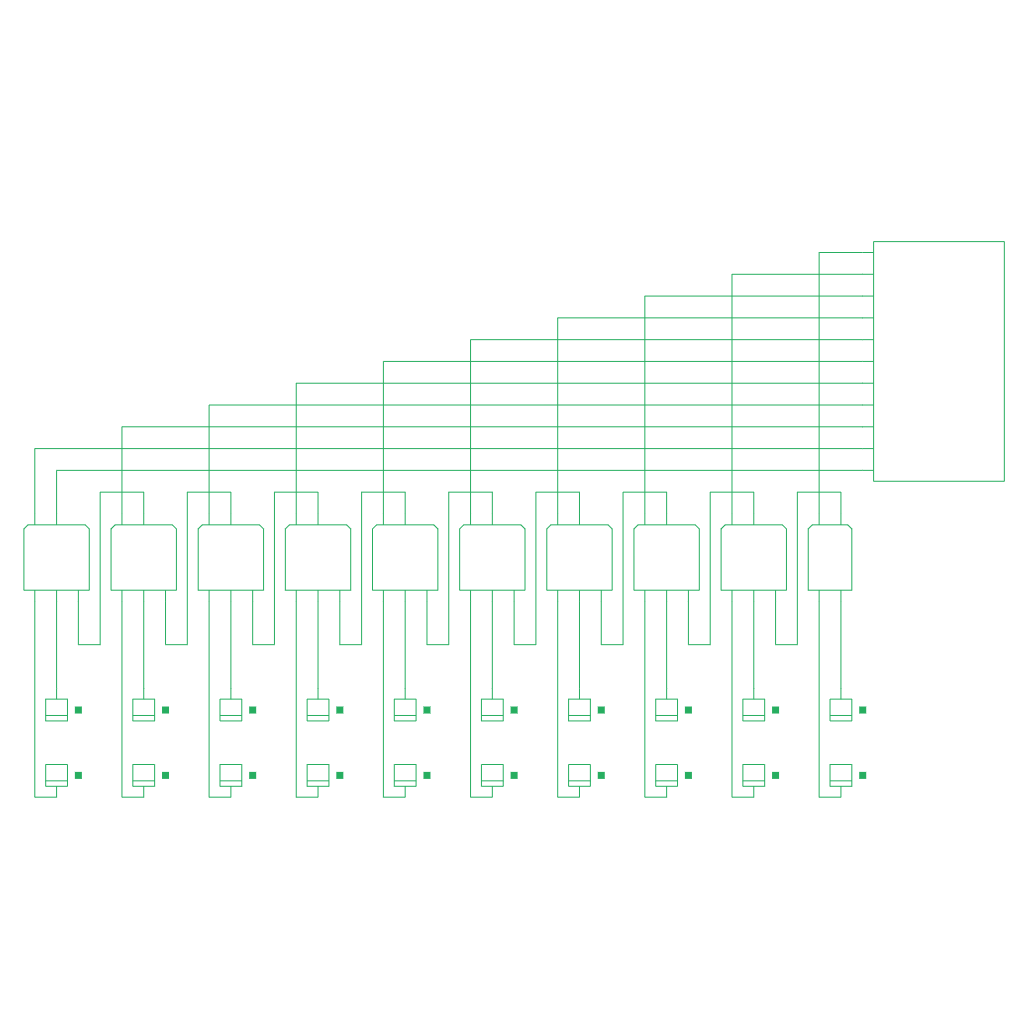

1. Allgemeine Beschreibung

Diese Schaltung ist ein 9-Bit-Binär-Addierer, der zwei 9-Bit-Zahlen addiert. Da 512 im Binärsystem 100000000₂ entspricht, benötigen wir 9 Bits, um beide Eingangsgrößen (bis 512) und das mögliche Übertragsbit zu berücksichtigen.

2. Aufbau der Schaltung

Die Schaltung basiert auf einer Kombination aus Halbaddierern (HA) und Volladdierern (FA):

Bit 0 (LSB - niederwertigstes Bit): Wird mit einem Halbaddierer (HA) berechnet, da kein Eingangsübertrag vorhanden ist.

Bit 1 bis 8: Werden mit Volladdierern (FA) realisiert, da sie einen möglichen Übertrag vom vorherigen Bit erhalten.

Übertragsbit (Carry-Out): Falls die Summe größer als 1023 ist, wird ein Carry-Out erzeugt.

3. Funktionsweise

Die zwei 9-Bit-Binärzahlen werden parallel in die Addierstufen eingegeben.

Jeder Bit-Addierer verarbeitet seine beiden Eingangswerte sowie ggf. einen Übertrag aus der vorherigen Stufe.

Die Ergebnisse aller Bit-Addierer bilden die 9-Bit-Summe.

Falls das Carry-Out-Bit gesetzt ist, bedeutet das, dass das Ergebnis 1024 oder größer ist.

4. Logische Komponenten

1 Halbaddierer (HA) für Bit 0

8 Volladdierer (FA) für Bit 1 bis 8

1. Allgemeine Beschreibung

Diese Schaltung ist ein 9-Bit-Binär-Addierer, der zwei 9-Bit-Zahlen addiert. Da 512 im Binärsystem 100000000₂ entspricht, benötigen wir 9 Bits, um beide Eingangsgrößen (bis 512) und das mögliche Übertragsbit zu berücksichtigen.

2. Aufbau der Schaltung

Die Schaltung basiert auf einer Kombination aus Halbaddierern (HA) und Volladdierern (FA):

Bit 0 (LSB - niederwertigstes Bit): Wird mit einem Halbaddierer (HA) berechnet, da kein Eingangsübertrag vorhanden ist.

Bit 1 bis 8: Werden mit Volladdierern (FA) realisiert, da sie einen möglichen Übertrag vom vorherigen Bit erhalten.

Übertragsbit (Carry-Out): Falls die Summe größer als 1023 ist, wird ein Carry-Out erzeugt.

3. Funktionsweise

Die zwei 9-Bit-Binärzahlen werden parallel in die Addierstufen eingegeben.

Jeder Bit-Addierer verarbeitet seine beiden Eingangswerte sowie ggf. einen Übertrag aus der vorherigen Stufe.

Die Ergebnisse aller Bit-Addierer bilden die 9-Bit-Summe.

Falls das Carry-Out-Bit gesetzt ist, bedeutet das, dass das Ergebnis 1024 oder größer ist.

4. Logische Komponenten

1 Halbaddierer (HA) für Bit 0

8 Volladdierer (FA) für Bit 1 bis 8

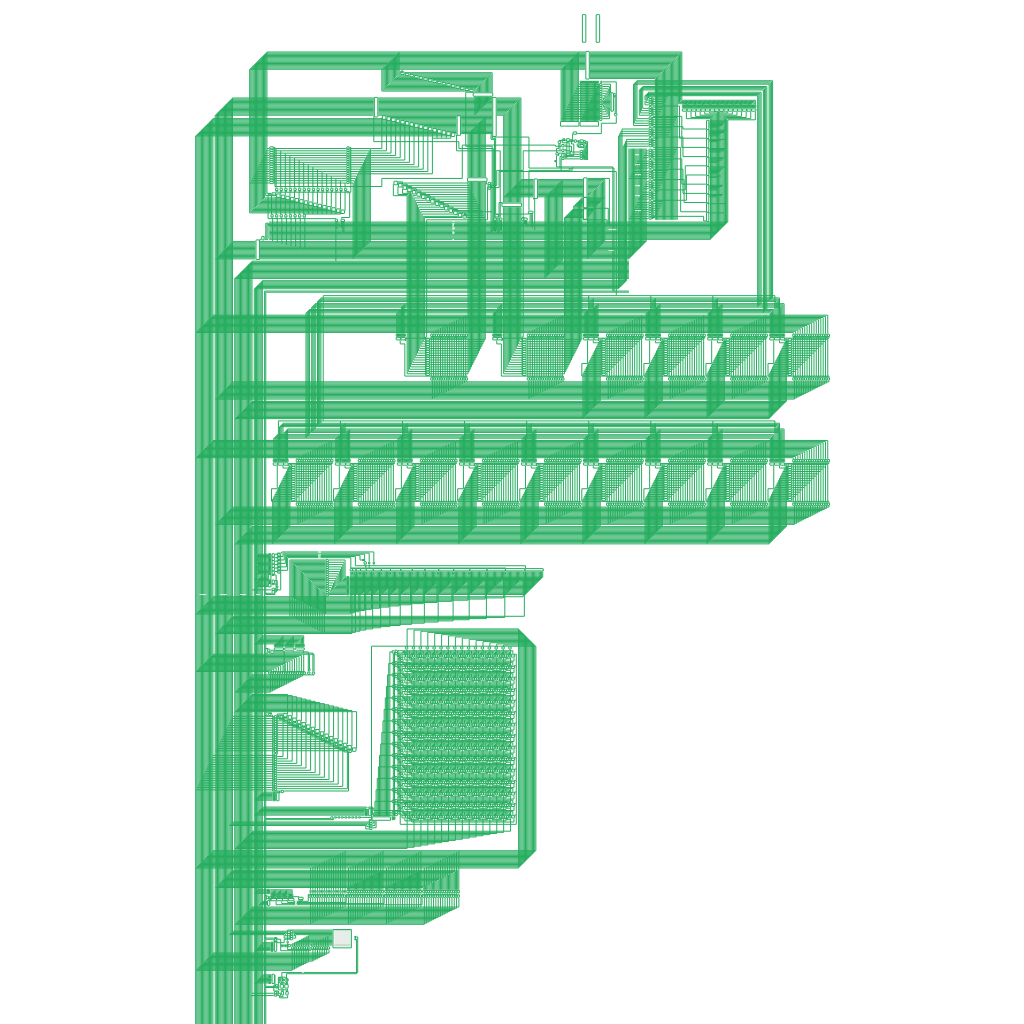

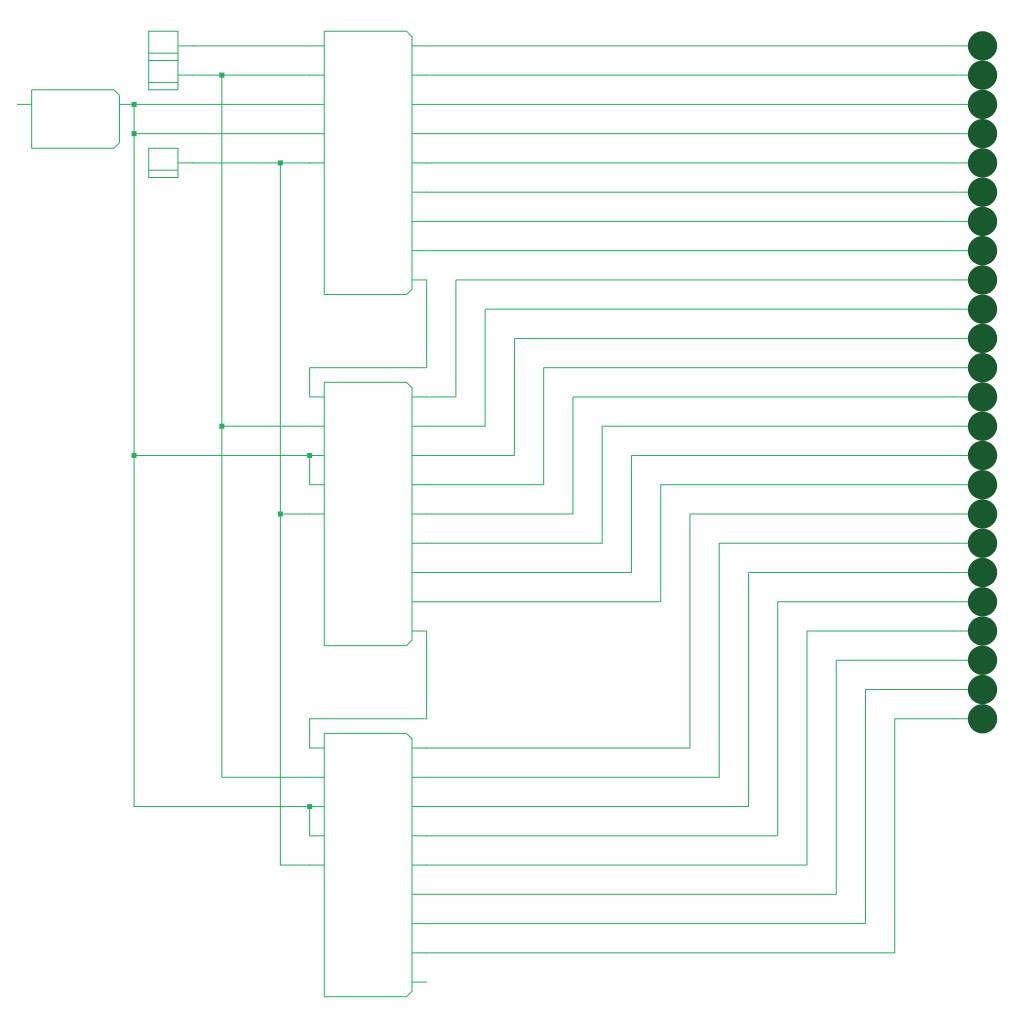

Runlight with 74HC595

Press SER-Button to Insert Data.

Set nCLR on Hight.

nOE on Low, to activate.